اولین راهکار اتصال نوری مبتنی بر TSMC COUPE برای تراشههای هوش مصنوعی نسل بعدی به نمایش گذاشته شد

در همایش OIP اروپایی TSMC در این هفته، Alchip و Ayar Labs یک موتور ورودی/خروجی نوری کاملاً یکپارچه و درونبستهای را به نمایش گذاشتند که بر پایه پلتفرم COUPE شرکت TSMC ساخته شده و اتصال نوری را برای شتابدهندههای هوش مصنوعی نسل بعدی فراهم میکند. این راهکار — که آیسی TeraPHY فوتونیک سیلیکونی Ayar را با دای رابط الکتریکی Alchip و یک کانکتور فیبر جداشدنی ترکیب میکند — میتواند تا 100 ترابیت بر ثانیه پهنای باند برای هر شتابدهنده ارائه دهد و با استفاده از رابط استاندارد صنعتی UCIe به تراشههای دیگر متصل شود. این راهکار برای توسعهدهندگان سختافزار که به اتصال نوری نیاز دارند اما نمیتوانند زیرسیستم نوری خود را از ابتدا بسازند، طراحی شده است.

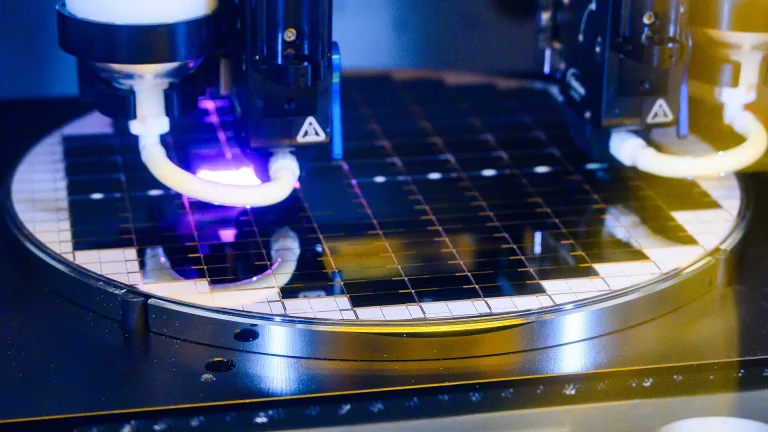

هنگامی که TSMC چارچوب موتور فوتونیک جهانی فشرده (COUPE) خود را در سال 2024 معرفی کرد، این شرکت عمدتاً توسعهدهندگان بزرگ تراشه مانند AMD یا Nvidia را هدف قرار داد که میتوانند مدارهای مجتمع الکترونیکی (EIC) و مدارهای مجتمع فوتونیک (PIC) خود را بسازند و سپس به TSMC سفارش دهند تا آنها را تولید کند.

با این حال، بسیاری از طراحان شتابدهندههای سفارشی منابع لازم برای یکپارچهسازی عمودی را ندارند (برخلاف Nvidia که کل پشته فناوریها — از محاسبات گرفته تا اتصال مقیاسپذیر — را با پلتفرمهای NVL72، NVL144 و NVL576 خود کنترل میکند) و تمایل دارند هر آنچه را که میتوانند مجوز بگیرند و سپس بر توسعه IPهایی تمرکز کنند که راهکار آنها را از دیگران متمایز میکند. اینجاست که زیرسیستم نوری آماده تولید از Alchip و Ayar Labs وارد عمل میشود و به طراحان تراشههای کوچکتر امکان میدهد تا اتصال نوری را به راحتی و بدون سرمایهگذاری دهها میلیون دلاری اولیه به تراشههای خود اضافه کنند.

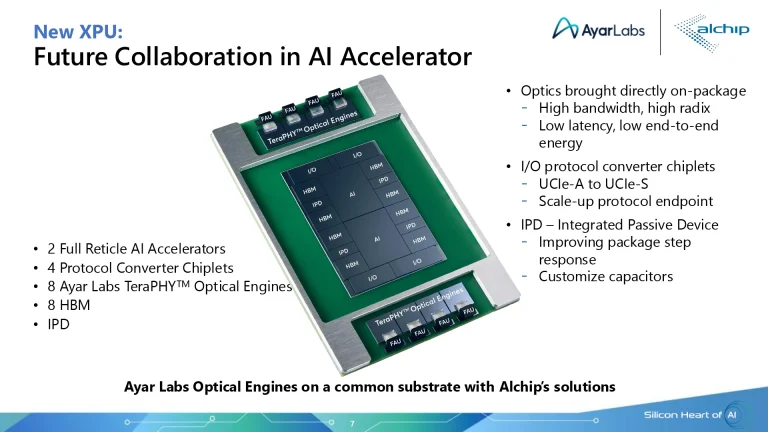

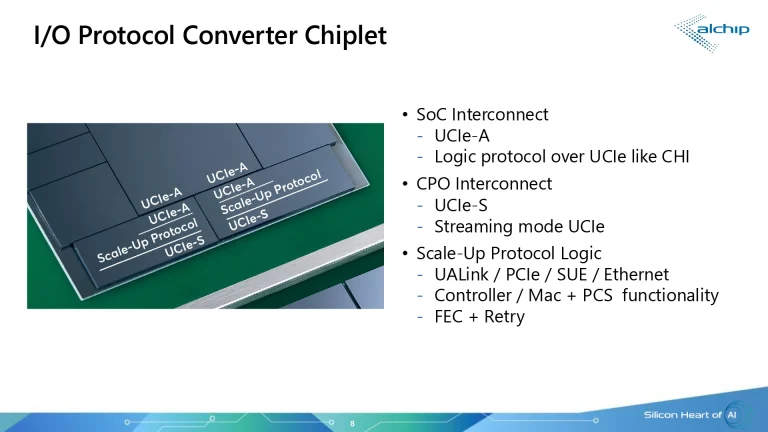

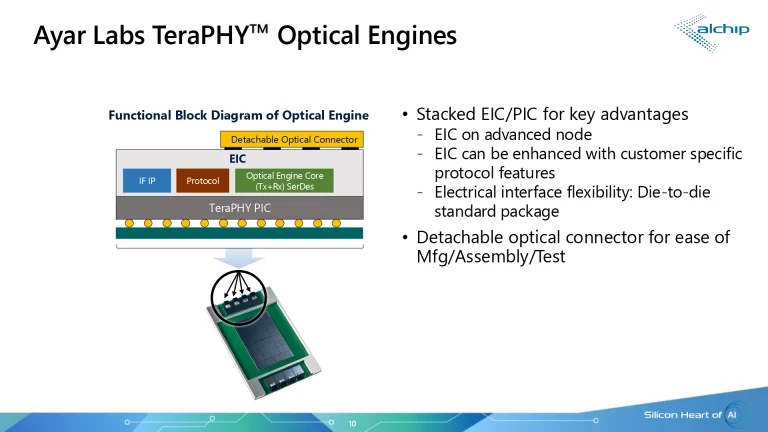

راهکار توسعهیافته مشترک توسط Alchip و Ayar Labs یک زیرسیستم ورودی/خروجی نوری سهچیپلت بستهبندیشده مشترک است که شامل یک چیپلت مبدل پروتکل Alchip UCIe-A به UCIe-S است که رابط UCIe-A شتابدهنده را خاتمه میدهد و پروتکلهای مقیاسپذیری (UALink, PCIe, Ethernet, SUE) را از طریق UCIe-S (جریانسازی) پیادهسازی میکند، یک EIC از Alchip که SerDes کممصرف، درایورهای مدولاسیون، زمانبندی و کنترل را فراهم میکند، و یک PIC TeraPHY از Ayar Labs که مدولاسیون و تشخیص نوری را با استفاده از فوتونیک سیلیکونی انجام میدهد.

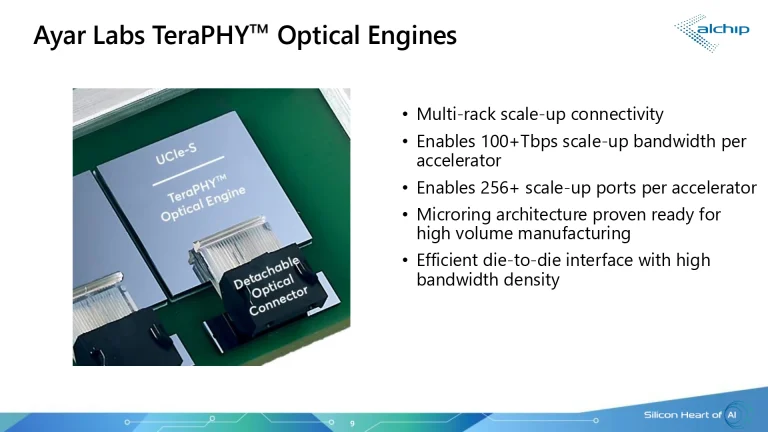

مبدل پروتکل Alchip همچنین میتواند پروتکلهای غیر UCIe را که بر روی رابط فیزیکی UCIe کپسوله شدهاند، حمل کند، بنابراین میتواند با دایهای محاسباتی که از پروتکلهای اختصاصی استفاده میکنند، کار کند. PIC از معماری میکرورینگ استفاده میکند و با کانکتورهای فیبر جداشدنی برای قابلیت ساخت ارائه میشود و دو گزینه لینک را ارائه میدهد: PAM4 CWDM (100–200 نانوثانیه در هر هاپ، BER < 10⁻⁶) و یک DWDM fast-follower (20–30 نانوثانیه در هر هاپ، BER < 10⁻¹²).

این زیرسیستم نوری میتواند به مقیاسپذیری فوقالعادهای دست یابد و از 100+ ترابیت بر ثانیه پهنای باند برای هر شتابدهنده و 256+ پورت نوری در هر دستگاه پشتیبانی کند تا صدها پردازنده را در چندین رک به هم متصل کرده و آنها را به عنوان یک پردازنده بزرگ واحد عمل کند. همچنین، شرکتها پیشبینی میکنند که راهکار آنها میتواند برای توسعهدهندههای حافظه نیز استفاده شود.

طراحی مرجع (یک ماکت) شامل دو دای شتابدهنده کامل، هشت پشته HBM، چهار چیپلت مبدل پروتکل و هشت موتور نوری TeraPHY از Ayar Labs است که همگی بر روی یک زیرلایه واحد با دستگاههای پسیو یکپارچه برای یکپارچگی توان نصب شدهاند. نمودارهای سیستمی Alchip نشان میدهند که این پلتفرم XPU را به XPU، XPU را به سوئیچ و سوئیچ را به سوئیچ متصل میکند و حتی امکان توسعه حافظه نوری را فراهم میآورد.

با استفاده از زیرسیستم Alchip که به صورت چیپلت فروخته خواهد شد، تقریباً هر توسعهدهنده شتابدهندههای هوش مصنوعی میتواند اتصالاتی با پهنای باند فوقالعاده بالا، تأخیر کم و بهرهوری انرژی در مقیاس رک و حتی چند رک را برای شتابدهندههای خود فراهم کند، که توسعه آن به صورت داخلی برای یک شرکت کوچک بسیار پرهزینه است.

- کولبات

- آذر 10, 1404

- 22 بازدید