اینتل فناوری ساخت بستههای چند-چیپلت فوقالعاده بزرگ را به نمایش میگذارد: ۱۲ برابر بزرگترین پردازندههای هوش مصنوعی، با شکست دادن بزرگترینهای TSMC

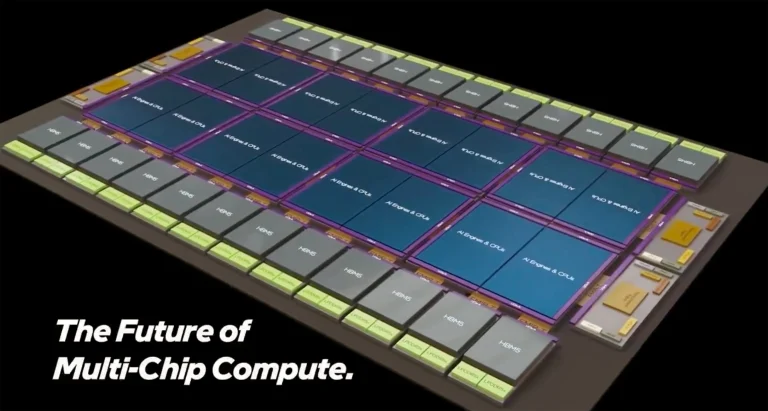

اینتل اولین شرکتی بود که یک طراحی چیپلت صریحاً تفکیکشده را با ۴۷ چیپلت، برای پردازنده گرافیکی محاسباتی Ponte Vecchio خود برای کاربردهای هوش مصنوعی و HPC ساخت. این محصول همچنان رکورد پرجمعیتترین طراحی چند-کاشی را در اختیار دارد، اما Intel Foundry چیزی به مراتب افراطیتر را متصور است: یک بسته چند-چیپلت که حداقل ۱۶ عنصر محاسباتی را در هشت دای پایه، ۲۴ پشته حافظه HBM5 ادغام میکند و تا ۱۲ برابر اندازه بزرگترین تراشههای هوش مصنوعی موجود در بازار (۱۲ برابر اندازه رتیکل، با شکست دادن رتیکل ۹.۵ برابری TSMC) مقیاسپذیر است. البته، ما فقط میتوانیم در مورد مصرف برق و الزامات خنککننده برای چنین پردازندههای قدرتمندی تعجب کنیم.

بسته مفهومی چند-چیپلت 2.5D/3D اینتل، ۱۶ عنصر محاسباتی بزرگ (موتورهای هوش مصنوعی یا CPU) را نشان میدهد که با فناوری فرآیند 14A اینتل یا حتی پیشرفتهتر 14A-E (کلاس ۱.۴ نانومتری، ویژگیهای بهبود یافته، ترانزیستورهای گیت-همه-جانبه RibbonFET 2 نسل دوم، و تحویل برق از پشت PowerVia Direct بهبود یافته) تولید شدهاند.

این عناصر بر روی هشت دای پایه محاسباتی (احتمالاً به اندازه رتیکل) قرار میگیرند که با فناوری 18A-PT (کلاس ۱.۸ نانومتری، با عملکرد بهبود یافته از طریق TSVها و تحویل برق از پشت) ساخته شدهاند و میتوانند کارهای محاسباتی اضافی انجام دهند یا مقدار زیادی حافظه کش SRAM برای دایهای محاسباتی ‘اصلی’ فراهم کنند، همانطور که اینتل در مثال خود نشان میدهد.

*برای تماشای ویدیوی پرواز، توییت بالا را باز کنید.

دایهای پایه با استفاده از Foveros Direct 3D به کاشیهای محاسباتی متصل میشوند، که از اتصال هیبریدی مس به مس با چگالی فوقالعاده بالا و زیر ۱۰ میکرومتر برای ارائه حداکثر پهنای باند و توان به دایهای بالایی بهره میبرد. Foveros Direct 3D اینتل در حال حاضر اوج نوآوریهای بستهبندی Intel Foundry است که بر طراحی بسیار پیچیده تأکید دارد.

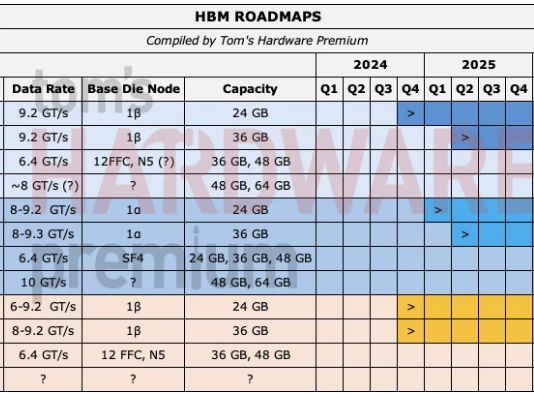

دایهای پایه از EMIB-T (نسخه بهبود یافته Embedded Multi-Die Interconnect Bridge با TSVها) به همراه UCIe-A در بالا، برای اتصالات جانبی (2.5D) بین خود و با دایهای ورودی/خروجی ساخته شده با فناوری 18A-P (کلاس ۱.۸ نانومتری، با عملکرد بهبود یافته) و دایهای پایه سفارشی، برای حداکثر ۲۴ پشته حافظه HBM5 استفاده میکنند.

قابل توجه است که اینتل پیشنهاد میکند از EMIB-T با UCIe-A در بالا برای اتصال ماژولهای HBM5 سفارشی استفاده کند، به جای استفاده از پشتههای HBM5 استاندارد JEDEC با رابط استاندارد صنعتی، احتمالاً برای دستیابی به عملکرد و ظرفیت بیشتر. با توجه به ماهیت مفهومی این نمایش، استفاده از پشتههای HBM5 سفارشی یک الزام طراحی نیست؛ بلکه صرفاً راهی برای نشان دادن این است که اینتل چنین دستگاههایی را نیز ادغام میکند.

کل بسته همچنین میتواند شامل PCIe 7.0، موتورهای نوری، شبکههای غیرهمدوس، SerDes 224G، شتابدهندههای اختصاصی برای مواردی مانند امنیت، و حتی حافظه LPDDR5X برای ظرفیت DRAM اضافی باشد.

توجه داشته باشید که ویدیوی منتشر شده توسط Intel Foundry در X، دو طراحی مفهومی را نشان میدهد: یکی ‘مقیاس متوسط’ با چهار کاشی محاسباتی و ۱۲ HBM، و دیگری ‘افراطی’ با ۱۶ کاشی و ۲۴ پشته HBM5، که داستان ما بر روی آن تمرکز دارد. حتی طراحی مقیاس متوسط نیز با استانداردهای امروزی بسیار پیشرفته است، اما اینتل میتواند آن را امروز تولید کند.

در مورد مفهوم افراطی، این ممکن است تا پایان دهه ظاهر شود، زمانی که اینتل نه تنها فناوری بستهبندی Foveros Direct 3D بلکه گرههای تولید 18A و 14A خود را نیز به کمال رسانده باشد. توانایی تولید چنین بستههای افراطی در اواخر دهه، اینتل را همتراز با TSMC قرار خواهد داد، که برنامههای مشابهی دارد و حتی انتظار دارد حداقل برخی از مشتریان از پیشنهادات ادغام در اندازه ویفر آن در حدود سالهای ۲۰۲۷-۲۰۲۸ استفاده کنند.

تبدیل طراحی افراطی به واقعیت در تنها چند سال یک چالش مهم برای اینتل است، زیرا باید اطمینان حاصل کند که قطعات هنگام اتصال به مادربردها تاب نمیخورند و حتی با حداقل تلرانسها به دلیل گرمای بیش از حد پس از استفاده طولانی مدت تغییر شکل نمیدهند. فراتر از آن، اینتل (و کل صنعت) باید یاد بگیرند که چگونه طرحهای پردازنده هیولایی به اندازه یک گوشی هوشمند (تا ۱۰,۲۹۶ میلیمتر مربع) را که بستهبندی حتی بزرگتری خواهند داشت، تغذیه و خنک کنند، اما این یک داستان دیگر است.

- کولبات

- دی 5, 1404

- 16 بازدید